计算机组成原理-学习笔记16-CPU控制器

计算机组成原理-学习笔记16-CPU控制器

1.处理器的结构

CPU的进一步分解:

image-20230210165711708

image-20230210165711708

细黑线:CPU内部总线

灰线:控制通路

1.1寄存器分类

上节偏重逻辑,这节偏重硬件

用户可见寄存器

- 允许编程人员通过机器语言或汇编语言访问,通过优化寄存器的使用而减少对主存的访问

控制和状态寄存器

- 由控制器来控制CPU的操作,并由拥有特权的操作系统程序来控制程序的执行

- 大多数控制和状态寄存器在大多数机器上是用户不可见的

- 某些在控制或操作系统模式下执行的机器指令是用户可见的

以上两者界限不明确

用户可见寄存器

类型:

- 通用寄存器(general-purpose register)

- 可被程序员指派各种用途

- 数据寄存器(data register)

- 仅可用于保持数据而不能用于操作数地址的计算

- 地址寄存器(address register)

- 可以是自身有某些通用性,或是专用于某种具体的寻址方式

- 例如:段指针、变址寄存器、栈指针

- 条件码寄存器(condition codes register) / 标志(flag) 寄存器

- CPU硬件设置这些条件位作为操作的结果,也可以是控制寄存器

- 至少是部分用户可见的 (隐含读出)

- 并不是必须的

设计的考量:

- 使用完全通用的寄存器还是规定各寄存器的用途

- 影响指令集的设计

- 寄存器数量

- 太少的寄存器会导致更多的存储器访问

- 太多的寄存器又不能进一步减少存储器访问

- 寄存器长度

- 应能保存大多数数据类型的值

- 某些机器允许两个相邻的寄存器作为一个寄存器来保持两倍长度的值

保存与恢复:

- 子程序调用会导致自动保存所有用户可见的寄存器,并在返回时自动取回

- 这些保存和恢复是作为调用和返回指令执行功能的一部分,由CPU完成

- 这允许各个子程序独立地使用用户可见寄存器

- 子程序调用之外保存用户可见寄存器的相关内容是程序员的责任,需要在程序

中为此编写专门的指令

控制和状态寄存器

类型:

- 程序计数器(Program counter, PC)

- 存有待取指令的地址

- 通常在每次取指令之后, PC的内容即被CPU更改,转移或跳步指令也会修改PC的内容,因此总指向将被执行的下一条指令

- 指令寄存器(Instruction register, IR)

- 存有最近取来的指令,在其中分析操作码和操作数

- 存储器地址寄存器(Memory address register, MAR)

- 直接与地址总线相连,存有存储器位置的地址

- 存储器缓冲寄存器(Memory buffer register, MBR)

- 直接与数据总线相连,存有将被写入存储器的数据字或从存储器读出的字,用户可见寄存器再与MBR交换数据

- ALU可对MBR和用户可见寄存器直接存取

程序状态字:

一个或一组包含状态信息的寄存器, 包含条件码加上其他状态信息

- 包含的字段或标志:(略?)

- 符号位 :容纳算术运算结果的符号位

- 零:当结果是0时被置位

- 进位carry:若操作导致最高位有向上的进位(加法) 或借位(减法) 时被置位, 用于多字算数运算

- 等于位:若逻辑比较的结果相等, 则置位

- 溢出位:用于表示算术溢出

- 中断允许/禁止位:用于允许或禁止中断

- 监管位:指出CPU是执行在监管模式中还是在用户模式中

其他:

指向含有附加状态信息的存储器块的指针寄存器

在使用向量式中断的机器中, 可能提供有一个中断向量寄存器

若栈用于实现某些功能, 需要有一个系统栈指针

对于虚拟存储器系统, 会有一个页表指针寄存器

设计出发点:

- 对操作系统的支持

- 某些类型的控制信息是专门为操作系统使用的

- 控制信息在寄存器和存储器之间的分配

- 一种普遍的做法是将存储器最前面(最低地址) 的几百或几千个字用于控制目的

- 在成本和速度之间进行权衡

2.微操作

回顾:

数据流

指令周期

子周期:取指周期、间址周期、执行、中断

本节:如何控制各种组件完成数据流功能

定义:每个子周期由一系列涉及CPU寄存器操作的更小步骤组成,这些步骤称为微操作

2.1 取指周期微操作

image-20230210173811498

image-20230210173811498

PC->MAR是指令地址

Mem->MBR->IR是指令内容

- 为什么t2/t3有两个操作:因为微操作互不冲突

- 微操作不是唯一的,例如PC+1放在t2和t3都可以

微操作分组原则

- 事件的流动顺序必须是恰当的

- 例: MAR <- (PC) 必须先于MBR <- 内存, 因为内存读操作要使用MAR中的地址

- 必须避免冲突(出现同一寄存器)

- 例: MBR <- 内存 和IR <- MBR 这两个微操作不应出现在同一时间单位里

- 满足上述条件下, 所用的时间单位尽可能少

- 例: PC <- (PC) + I不能放在一个单独的时间单位里成为t4

2.2 间址周期微操作

image-20230210181035586

image-20230210181035586

t1:取数据地址

t2:取数据

t1和t2不能调换

2.3 执行周期

image-20230210181148727

image-20230210181148727

都不能再压缩

ADD:取操作数X,与R1加

BSA:存原地址到MBRhe1Mem,取新地址到MAR和PC

2.4中断周期

image-20230210181944789

image-20230210181944789

中断周期的任务:处理中断请求。需保存旧地址和旧地址内容

存旧地址到主存和MAR,旧地址内容到MBR,新地址到PC

2.5 指令周期代码(把微操作连起来)

取指、间址、中断周期各有一个微操作序列,执行周期则对于每个操作码有一个微操作序列

指令周期代码ICC:

假设一个2位的ICC寄存器,明确CPU处于指令周期哪个阶段

刚好4种状态

image-20230210182613175

image-20230210182613175

间接周期、执行周期、中断周期都类似上图。

3.CPU内部控制

3.1 门管理实例

ALU和寄存器都连接到CPU内部总线上

内部总线和寄存器之间有门和控制信号

控制线控制着数据和系统总线(外部)的交换以及ALU的操作

例子: image-20230210202037860

image-20230210202037860

Y、Z用来暂存,因为总线不能同时传两个数据。

每次开两个门(一入一出)

3.2 控制CPU的功能需求

- CPU的基本元素

- ALU,寄存器组,内部数据通路,控制器,外部数据通路

- CPU需要完成的微操作(内外 )

- 在寄存器之间传送数据

将数据由寄存器传送到外部接口(如系统总线)

将数据由外部接口传送到寄存器

将寄存器作为输入和输出,完成算术和逻辑运算

- 在寄存器之间传送数据

- 控制器的两个基本任务

- 定序(sequencing) :根据正被执行的程序,控制器使CPU以正确的顺序通过一系列微操作

- 执行(execution) :控制器使每个微操作得以完成

3.3 控制器的输入输出

image-20230210203112589

image-20230210203112589

输入:

- 指令寄存器: 当前指令的寻址方式(决定有无间址周期)和操作码(决定微操作)

- 标志: 确定CPU的状态和前一个ALU操作的结果

- 时钟: 控制器要在每个时钟脉冲完成一个或一组同时的微操作

- 来自控制总线的控制信号: 向控制器提供控制信号

- 控制器一般为主动输出。偶尔为被动

- 例:中断请求

输出:

- CPU内的控制信号:

- 用于寄存器之间传送数据

- 用于启动特定的ALU功能

- 到控制总线的控制信号:

- 到存储器的控制信号

- 到I/O模块的控制信号

所有的控制信号最终作为二进制输入量(0/1)直接输入到各个逻辑门上

样例

取指周期

image-20230210204128417

image-20230210204128417

间接取指、中断

image-20230210204200945

image-20230210204200945

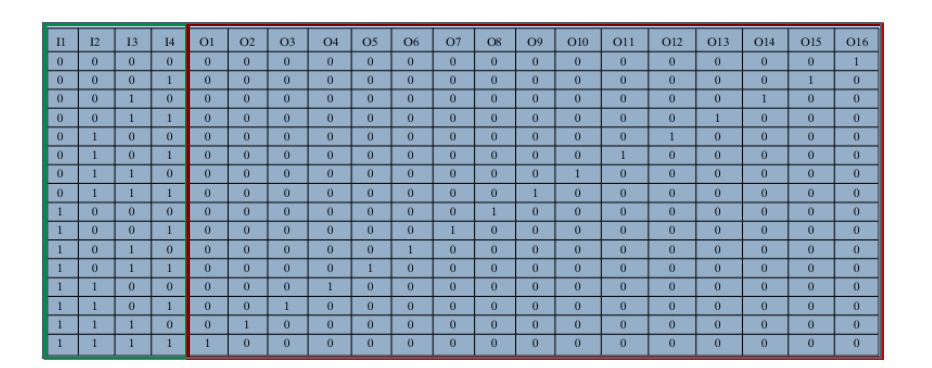

3.4 控制器的细节实现

控制器的最小特性 :

- 它只需要知道将被执行的指令和算术、逻辑运算结果的性质(如正负、溢出等),而不需要知道正被处理的数据或得到的实际结果具体是什么(交由ALU)

- 它只是以少量的送到CPU内的和送到系统总线上的控制信号来实现控制

即:尽可能简洁

硬布线实现(hardwired implementation):

控制器是一个组合电路,把输入逻辑信号通过硬件转换为一组输出逻辑信号,即控制信号

标志和控制总线信号

指令寄存器

- 通过译码,使每一操作码有一个唯一的逻辑输入

- 译码器有 n 个输入和 2^𝑛个输出

- 控制器要考虑变长的操作码,译码器会更复杂些

image-20230210205002992

image-20230210205002992时钟

- 在一个指令周期(子周期)内,控制器要在不同时间单位发送不同的控制信号

- 使用一个定时器作为控制器的输入,并且控制器在指令周期(或子周期)结束时必须通知定时器以使其重新开始计数

image-20230210205421295

image-20230210205421295

硬布线控制的逻辑本质:为每个输出的控制信号设计一个关于控制器输入的布尔表达式

image-20230210205450049

image-20230210205450049

微程序(固件)实现(microprogrammed implementation):

基本概念:

- 控制逻辑是微程序指定的,控制器是一个相对简单的逻辑电路,通过执行每条微指令来产生控制信号

- 微程序(固件) 介于硬件与软件之间

- 设计固件比设计硬件容易,但写固件程序比软件程序困难

- 微指令序列

- 微指令: 每行描述一个时间内出现的一组微操作

基本思路:

- 对于每个微操作,控制器的任务是产生一组控制信号,即控制器发出的每根控制线或开或关(每根控制线由一个二进制数字表示)

- 构造一个控制字,每位代表一根控制线,这样每个微操作能用控制字中的不同的0和1的样式来表示

- 将这些控制字串在一起,可以表示控制器需要完成的微操作序列

具体实现:

- 由于微操作序列不是固定的,把控制字放入一个存储器单元中, 每个字有自己唯一的地址

- 添加少数几位用于指示条件的真假

- 若条件位指示的条件为假,则顺序执行下一条指令

- 若条件位指示的条件为真,则地址字段指向的微指令是将被执行的下一条微指令

image-20230210210755662

image-20230210210755662

(长短表示控制字种类多少)

微程序宏观执行:

image-20230210211308771

image-20230210211308771

任务:

- 定序(microinstruction sequencing)

- 根据当前的微指令、 条件标志和指令寄存器的内容, 产生下一微指令的控制存储器地址

- 设计考虑

- 微指令的大小:减小微指令的大小就能节省控制存储器的成本

- 地址生成时间:尽可能快地执行微指令

- 执行(microinstruction execution)

- 产生控制信号:发往CPU内部, 送往外部控制总线或其他外部接口

- 根据微指令中的二进制序列, 设置控制线

- 产生控制信号:发往CPU内部, 送往外部控制总线或其他外部接口

定序细节

多种地址格式:

image-20230210212031773

image-20230210212031773

单地址较常用。

定序逻辑构成细节:

image-20230210212057060

image-20230210212057060

微程序控制流程

image-20230210212734243

image-20230210212734243

- 生成新地址的三个选择 :

- 取顺序下一条微指令:加1到控制地址寄存器

- 基于跳转微指令转移到一个新的例程:将控制缓冲寄存器的地址字段装入控制地址寄存器

- 转移到一个机器指令例程:根据IR中的操作码向控制地址寄存器装入机器指令例程的第一条微指令

image-20230210230355597

image-20230210230355597

微程序设计优缺点:

- 简化了控制器的设计任务

- 实现起来既成本较低,也能减少出错机会

- 便于更新

- 缺点:要比采用相同或相近半导体工艺的硬布线控制器慢一些